reverse engineering and exploiting the shannon baseband

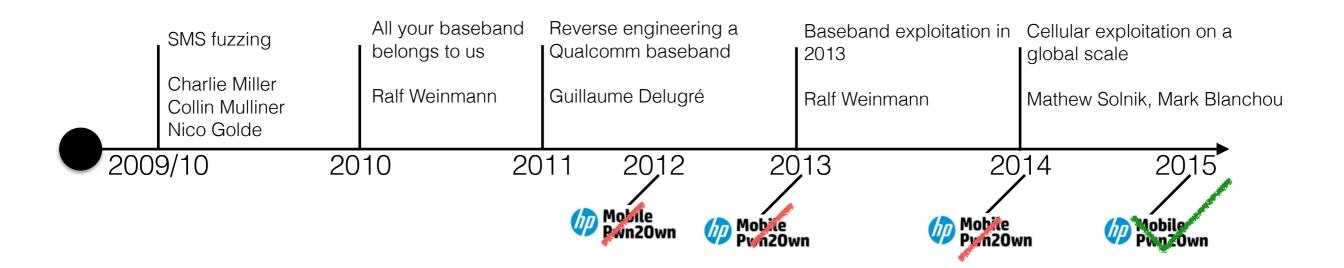

### Motivation

- little concrete/reproducible work on analyzing and exploiting cellular basebands

- lots of protocol research: Benoit Michau, Ravi Borgaonkar, SRLabs, Osmocom,...

- everyone keeps talking about this / lots of FUD (hi OSnews!)

- highest payout at mobile pwn2own historically (100-150k\$)

### Motivation cont.

- most research focused on Qualcomm basebands (AMSS)

- but we worked for Qualcomm:)

- QC lost significant market share with release of Samsung Galaxy S6/Edge

- S6\* became pwn2own target

- Shannon: how hard can it be?

this is our story from 0 to 0-day

### Talk Structure

- Steps to reverse engineer the RTOS, find vulns, and write a full RCE exploit

- We try to reconstruct our path, including both successes and fails

- We release all our custom-built RE tools \o/

# Shannon Background

- Samsung's own(?) cellular processor (CP)/modem/baseband implementation

- entire mobile phone stack (2-4G, SIM, IPC with application processor OS, ...)

- not new at all

- Galaxy S5 mini, Galaxy Note 4, various Samsung USB LTE sticks (e.g. GT-B3740)

- non-Samsung devices

- e.g. some Meizu smartphone models

- ... and still used by Samsung!

- most non-US Galaxy S7 devices

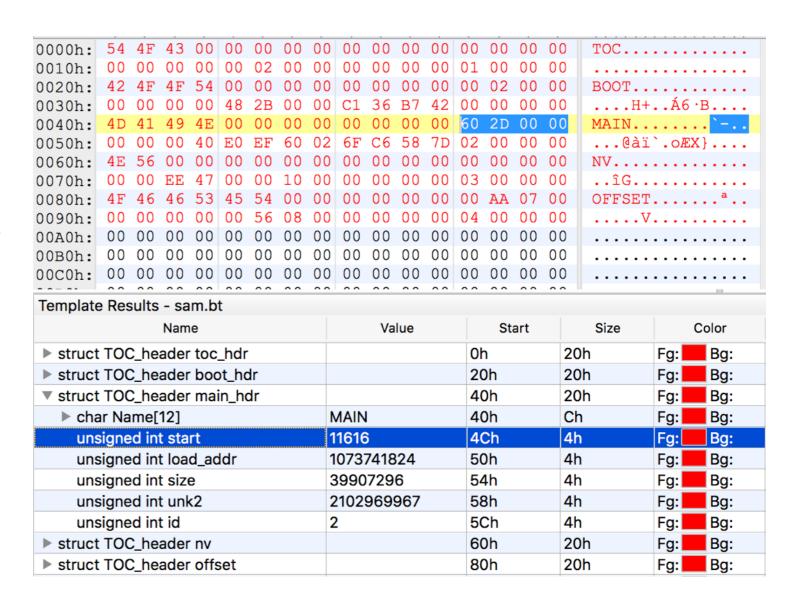

### Taking a Peek at Firmware

- modem.bin can be obtained from firmware images or Android RADIO device partition

- No luck on the naive approach:

# Identifying Code

- BOOT: baseband bootstrap code

- MAIN: baseband code

- NV: non-volatile memory - likely baseband settings etc

- OFFSET: unknown

- proprietary/undocumented header format

- contains some kind of hash / secure boot

# Identifying BOOT Code

```

00003f0: b503 00eb 8504 a0e3 1812 90e5 1822 90e5

0000400: 0f10 81<mark>e3</mark> 0210 81<mark>e1</mark> 1812 80<mark>e5</mark> 1215 a0<mark>e3</mark>

0000410: 0103 a0<mark>e3</mark> 8c08 00<mark>eb</mark> 5400 a0<mark>e3</mark> 9<mark>e0</mark>3 00<mark>eb</mark>

0000420: f301 00<mark>eb</mark> 4400 a0<mark>e3</mark> 9b03 00<mark>eb</mark> 0c04 00<mark>eb</mark>

. . . . D. . . . . . . . . . .

0000430: 1040 bd<mark>e8</mark> 0d0d 8f<mark>e2</mark> a303 00<mark>ea</mark> 1f40 2d<mark>e9</mark>

0000440: 8903 00eb cd0f 8fe2 9f03 00eb 3403 9fe5

0000450: 9d03 00<mark>eb</mark> 330e 8f<mark>e2</mark> 9b03 00<mark>eb</mark> fc0e 02<mark>e3</mark>

. . . . 3 . . . . . . . . . . .

0000460: 0000 90<mark>e5</mark> 2863 9f<mark>e5</mark> 0600 50<mark>e1</mark> 0600 001a

....(c....P.....

0000470: 2003 9f<mark>e5</mark> 7701 00<mark>eb</mark> 4200 a0<mark>e3</mark> 8603 00<mark>eb</mark>

...w...B.....

0000480: 5f01 00<mark>eb</mark> 6300 a0<mark>e3</mark> 8303 00<mark>eb</mark> 3008 00<mark>eb</mark>

_...c.....0...

00004a0: 7d03 00<mark>eb</mark> 2108 00<mark>eb</mark> 5300 a0<mark>e3</mark> 7a03 00<mark>eb</mark>

}...!...S...z...

00004b0: f602 00<mark>eb</mark> 4c00 a0<mark>e3</mark> 7703 00<mark>eb</mark> aaff ff<mark>eb</mark> ....L...w......

00004c0: 4700 a0<mark>e3</mark> 7403 00<mark>eb</mark> a602 00<mark>eb</mark> 6900 a0<mark>e3</mark> G...t...i...

00004d0: 7103 00<mark>eb</mark> c042 9f<mark>e5</mark> 0050 a0<mark>e3</mark> bc22 9f<mark>e5</mark>

```

E\* often tied to ARM condition codes -> actual code?

# Identifying BOOT Code

```

00003f0: b

0000400:

0000410:

; Attributes: noreturn

0000420:

sub_23C

var 18 = -0x18

0000430:

var 10 = -0x10

var C= -0xC

0000440:

STMFD

SP!, {R0-R4,LR}

BL

sub 106C

0000450:

RO, as333 ; "\ns333 ("

ADR

BL

sub 10CC

LDR

RO, =aFeb122015; "Feb 12 2015"

0000460:

..(c...P....

BL

sub 10CC

RO, asc_58C ; ") : "

ADR

sub 10CC

BL

..w...B....

0000470:

MOV

RO, #0x2EFC

LDR

RO, [RO]

0000480:

LDR

R6, = 0x424F4F54

CMP

RO, R6

BNE

loc 28C

0000490:

00004a0:

R0, =0x47900000

BL

sub 858

MOV

BL

00004b0:

R0, -\#0x42 ; 'B

sub 109C

BL

sub_804

00004c0:

MOV

R0, \#0x63 ; 'c'

BL

sub 109C

00004d0:

```

looks like sane ARM code!

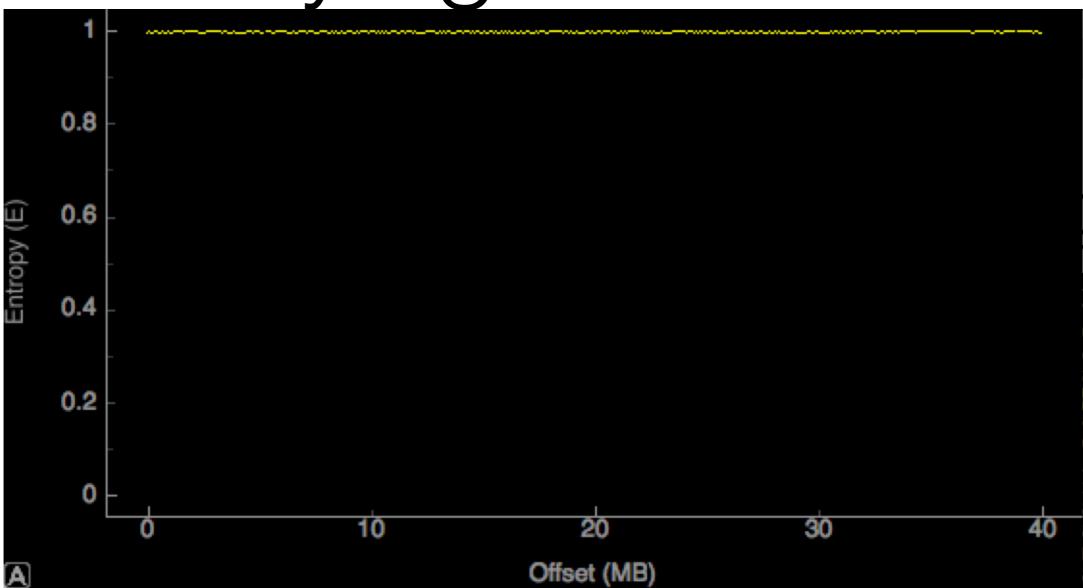

# Identifying MAIN Code

```

0006120: 5f<mark>a8</mark> b6d6 dcfe 207a 7<mark>e0</mark>4 7208 65bc <mark>e5</mark>71 _..... z~.r.e..q

0006130: d6<mark>e4 e7</mark>2c <mark>e7</mark>89 c8c8 bd47 f313 4b0a <mark>e1</mark>78 ...,....G..K..x

0006140: 7d6f 6226 6c46 f8de 66a9 bc96 5d4c cf7d }ob&lF..f...]L.}

0006170: df9b 3a75 b<mark>e5</mark>e 42c2 da<mark>eb</mark> daf8 f6fc 4b0d

..:u.^B.....K.

x.Nz.M..c.3....

0006180: 78da 4<mark>e7</mark>a 1d4d dd8a 63a3 33<mark>e2</mark> 12ba 81b8

0006190: c264 5f04 d557 08b7 fd89 7f75 <mark>ed</mark>99 ca0c

.d_..W....u...

00061a0: 249d 29bd 5001 a4cd <mark>e9</mark>51 0176 f06a 7dca

$.).P....Q.v.j}.

00061b0: 39d1 fc35 8c1e 1d86 25c2 d510 6271 8c47

9..5...%...bq.G

00061c0: 5fad ca73 83<mark>ea</mark> 802c 5<mark>ea</mark>6 b79d f45f 7fc5

_..s..,^...._.

.]....;n

00061d0: dc5d 8fcc c994 9<mark>e9</mark>d bf46 1cf4 cc92 3b6e

00061<mark>e0</mark>: 4b0c 4fba 0781 64c8 d44d 73<mark>e3</mark> 9a3f 0<mark>eb</mark>a  K.O...d..Ms..?..

00061f0: <mark>e9</mark>03 2b76 a9af b5ba ff66 983e 41f4 0601

..+v....f.>A...

0006200: 3<mark>ef</mark>0 6c<mark>e5</mark> 8b41 f934 7b2a 7142 dccc 77bf  >.l..A.4{*qB..w.

.....H..U....

0006220: ba84 4d6e 6416 b84a 0719 9f5d 0597 6b8a

..Mnd..J...]..k.

0006230: f663 4d51 c<mark>e4</mark>6 3<mark>e8</mark>0 f29a 3f25 13db 634f

.cMQ.F>...?%..c0

1006240: f3fa <mark>e4</mark>7f ddc6 64a2 c61b 6a42 fac0 c2d6

....d...jB....

```

- ~38 MB binary

- no such luck as before, no idea what this is

- Galaxy S6 image the first to feature this

Identifying MAIN Code

- constant high/flat entropy, likely encryption

- no silly xor encryption as far as we can tell

# MAIN Code: Remaining Options

- BOOT: tight copy/replace loops with hardware-assisted memory mapped-io -> hard

- TEE/TrustZone: Trustlets potentially involved in decryption -> dead end

- Android kernel/user space involvement (/sbin/cbd):

CP Boot Daemon / Cellular Baseband Daemon

- -> dead end

### CP Boot Daemon (cbd)

```

mif: cbd: prepare_boot_args: DEV(/dev/spi_boot_link) opened (fd 10)

mif: cbd: prepare_boot_args: BIN(/dev/block/platform/15570000.ufs/by-name/RADIO) opened (fd 11)

mif: cbd: prepare_boot_args: toc[0].name = TOC

mif: cbd: prepare_boot_args: toc[1].name = BOOT

mif: cbd: prepare_boot_args: toc[2].name = MAIN

mif: cbd: prepare_boot_args: toc[3].name = NV

mif: cbd: prepare_boot_args: NV(/efs/nv_data.bin) opened (fd 12)

```

- started at boot:

- parses modem image TOC

- sends modem via SPI\* for loading

- kernel driver assistance (see drivers/misc/modem\_v1/modem\_io\_device.c)

- no relevant unpacking/decrypting of image though

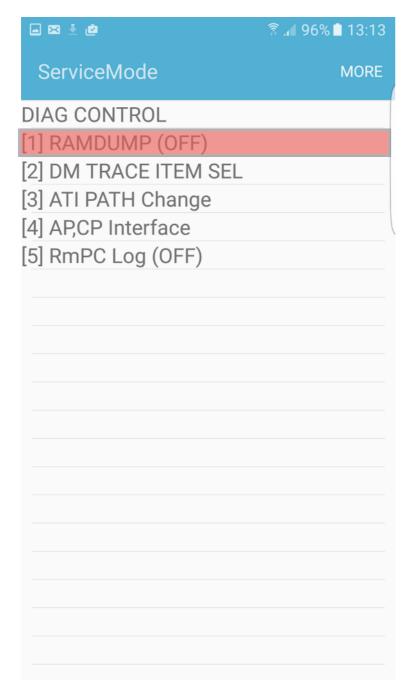

### Generating live RAMDUMPs

cbd/kernel code have code for ramdumps via:

```

/dev/umts_ramdump0

IOCTL_MODEM_RAMDUMP_START

```

can be triggered directly from cbd as root via -o u (test/ ramdump)

```

root@zerolte:/sdcard/log # ls -l

134656256 2015-05-31 20:29 cpcrash_dump_20150531-2050.log

-rwxrwx--- 1 root sdcard_r

512 2015-05-31 20:29 cpcrash_info_ss333_20150531-2050.log

sdcard_r

-rwxrwx--- 1 root

685 2015-05-31 20:29 cpcrash_log_20150531-2050.log

-rwxrwx--- 1 root sdcard_r

232312 2015-05-31 20:29 logcat_radio_20150531-2050.log

-rwxrwx--- 1 root sdcard_r

8388608 2015-05-31 20:29 mem_dump_20150531-2050.log

-rwxrwx--- 1 root sdcard_r

-rwxrwx--- 1 root sdcard_r

432 2015-05-31 20:29 mif_trace_201505312051_17.log

528719 2015-05-31 20:29 umts_crash_201505312051_17.log

-rwxrwx--- 1 root sdcard_r

```

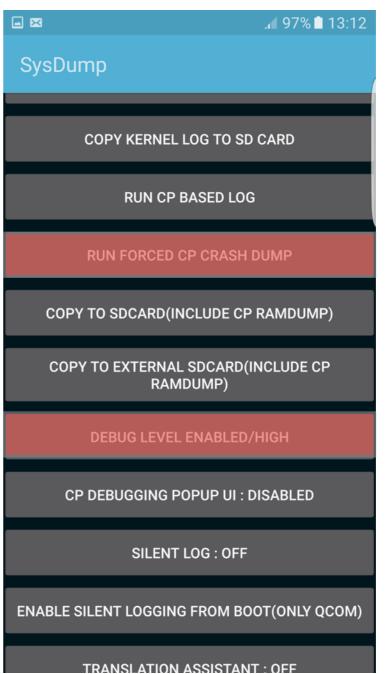

### UI-based RAMDUMPs

non-root (as we found later)

\*#9900#

# Interpreting RAMDUMP

- 130mb dump: containing code, but not continuous in memory -> analysis in IDA will be broken

- cbd<->boot knowledge brought us to ramdump handler in boot

```

8  dword_2948[0].start_ea = (void *)0x40000000;

9  dword_2948[0].size = 0x80000000;

10  dword_2948[1].start_ea = (void *)0x4000000;

11  dword_2948[1].size = 0x10000;

12  dword_2948[2].start_ea = (void *)0x4800000;

13  dword_2948[2].size = 0x4000;

14  dword_2948[3].start_ea = (void *)0xE00000000;

15  dword_2948[3].size = 0x57000;

16  dword_2948[4].start_ea = (void *)0x2F00;

17  dword_2948[4].size = 0x100;

```

can nicely translate into an IDA loader!

### Reverse Engineering Shannon

- 130MB ramdump (~38 code)

- ~70k functions

- stripped, but fairly verbose on strings

- ARM Cortex R7

- Goal:

- identify RTOS primitives

- identify cellular stack layers (Layer2/3 GSM,UMTS,LTE)

- find way to debug

- find exploitable OTA issues

```

SS333/SS310 DEVELOPMENT PLATFORM

- ARM Emulation Baseboard | Cortex-R7

- Software Build Date : %s

- Software Builder : %s

- Compiler Version : ARM RVCT %d.%d [Build %d]

Platform Abstraction Layer (PAL) Powered by

Modem H/W Lab BSP SW Part

```

```

C../../PSS/StackService/SMS/Code/Src/sms_PduCodec.c

../../PSS/StackService/SMS/Code/Src/sms_Utilities.c

A../../PSS/StackService/DS_SMS/Code/Src/ds_sms_Main.c

$A../../PSS/StackService/DS_SMS/Code/Src/ds_sms_Main.c

C../../PSS/StackService/DS_SMS/Code/Src/ds_sms_PduCodec.c

../../PSS/StackService/DS_SMS/Code/Src/ds_sms_Utilities.c

../../PSS/StackService/GMC/GmcF/code/src/Gmc_Timer.c

../../PSS/StackService/GMC/GmcF/code/src/Gmc_TraceLog.c

$A../../PSS/StackService/GMC/GmcF/code/src/Gmc_EventBus.c

../../PSS/StackService/GMC/GmcF/code/src/Gmc_Main.c

../../PSS/StackService/GMC/GmcF/code/src/Gmc_Main.c

```

### Sugar-coating MAIN Code

- We got the MAIN code, but:

- significant amount of unidentified code

- tons of strings to make use of

- RTOS identification cumbersome with stock IDA functionality

- debug capability needed for actual verification

### Assisting Function Detection

- IDA's 2 pass analysis is decent, but still misses lots of functions, confuses code/data segments

- Simple script to find function prologues improves upon IDA's results by thousands of functions

- False positives definitely exist, but hurt very little

# Making Use of Strings

- ~100k usable strings (common in basebands due to debug tools, e.g. Samsung DM)

- state strings

- file paths (hierarchical info)

- function names

any automatic labeling is better than sub\_\*!

```

GMM_TIMEROUT_ERR

GMM_LOW_LAYER_FAILURE_ERR

GMM_DETACH_BY_THE_NETWORK_ERR

GMM_AUTH_FAIL_ERR

GMM_AUTH_REJ_ERR

GMM_INCORRECT_STATE_ERR

GMM_USER_PLMN_SEL

GMM_SIM_CONSIDERED_INVALID_ERR

GMM_ACCESS_CLASS_NOT_ALLOWED

GMM_EST_REJ_TRY_OTHER_RAT

GMM_NORMAL_RELEASE

```

```

A../../HEDGE/NASL3/DS_MM/Code/Src/ds_mm_GmmPduCodec.c

../../../HEDGE/DS_GL3/GRR/Code/Src/ds_rr_tim.c

../../../CALPSS/LteL3/LteRrc/Code/src/LteRrc_CommUtil.c

A../../HEDGE/DS_GL3/GRR/Code/Src/ds_rr_resel.c

A../../HEDGE/DS_GL3/GRR/Code/Src/ds_rr_resel.c

<B../../HEDGE/DS_GL3/GRR/Code/Src/ds_rr_plmn.c

../../HEDGE/DS_GL2/GMAC/Code/Src/ds_mac_util.c

+;A../../../HEDGE/DS_GL2/GMAC/Code/Src/ds_mac_util.c

:;A../../../HEDGE/DS_GL3/GRR/Code/Src/ds_rr_list.c

A../../HEDGE/DS_GL3/GRR/Code/Src/ds_rr_list.c

```

### Strings->Function Label

#### "exact" strings

identify handlers with debug info

fatal\_error assert\_fatal free debug\_trace\_

function names

file names

path info (module)

#### "fuzzy/misc" strings

sanitize remaining strings

> 5 chars alphanumeric consonants vowels

# Applying Labels

- For each function:

- calls known API? -> trace back arguments -> label

- part of known directory structure? -> sanitize path -> partial label

- contains file name -> sanitize file -> sub module / partial label

- uses only fuzzy string? -> label

- reuse names for labeling callers of these functions -> "calls\_..."

- rinse and repeat every now and then

IDApython yields ~20k named functions

- misc\_ds\_ss\_SendUssdRegisterMsg\_something

- misc\_ds\_ss\_SendLcsRegisterMsg\_something

- f ds\_ss\_SendLcsMolrRsp

- f misc\_ds\_ss\_SendLcsNotifyIndMsg\_something

- f sms\_SendUbmcActivateDeactivateReqMsg

- f calls\_sms\_SendUbmcActivateDeactivateReqMsg\_\_2

- calls\_sms\_SendUbmcActivateDeactivateReqMsg\_\_3

- f sms\_SendCbInd

- f calls\_sms\_SendUbmcActivateDeactivateReqMsg

- f misc\_sms\_SendFailRspAndClearSession\_something

- f sms\_SendCellInfoReqMsg

- 0 15 0 5 14

### RTOS Primitive Identification

- In ARM, lot of RTOS primitives are implemented via system control coprocessor instructions (MCR/MRC)

- IDA doesn't parse these

- scripted MCR annotation: ARM R7, ARM9, and ARM11

```

.text:40E1CB74 disable instruction cache

; CODE XREF: initialize MPU config+6<sup>1</sup>p

p15, 0, R1,c1,c0, 0

.text:40E1CB78

BIC

R1, R1, #0x1000

MCR

.text:40E1CB7C

p15, 0, R1,c1,c0, 0; Write System Control Regi

.text:40E1CB80

ISB

.text:40E1CB84

End of function disable instruction cache

.text:40E1CB88

.text:40E1CB88

.text:40E1CB88

.text:40E1CB88

enable_instruction_cache

; CODE XREF: initialize MPU_config+86îp

.text:40E1CB88

.text:40E1CB8C

MCR

p15, 0, R0,c7,c5, 0; Invalidate entire instruc

MRC

p15, 0, R0,c1,c0, 0

.text:40E1CB90

ORR

.text:40E1CB94

RO, RO, #0x1000

.text:40E1CB98

MCR

p15, 0, R0,c1,c0, 0; Write System Control Regi

.text:40E1CB9C

ISB

.text:40E1CBA0

.text:40E1CBA0

End of function enable instruction cache

.text:40E1CBA0

.text:40E1CBA4

.text:40E1CBA4

.text:40E1CBA4

enable_instruction_and_data_cache

.text:40E1CBA4

.text:40E1CBA4

p15, 0, R1,c1,c0, 0

.text:40E1CBA8

ORR

R1, R1, #0x1000

.text:40E1CBAC

ORR

R1, R1, #4

.text:40E1CBB0

DSB

.text:40E1CBB4

MOV

.text:40E1CBB8

MCR

.text:40E1CBBC

MOV

p15, 0, R0,c7,c5, 0; Invalidate entire instruc

.text:40E1CBC0

MCR

MCR

p15, 0, R1,c1,c0, 0; Write System Control Regi

.text:40E1CBC4

.text:40E1CBC8

.text:40E1CBCC

; End of function enable_instruction_and_data_cache

.text:40E1CBCC

.text:40E1CBCC

```

### RTOS Baseline

- What privilege level are we running at?

- How to find/enumerate the tasks of the OS?

- How are tasks handled in this OS? Start-up, communication, separation?

- Memory management of tasks (heaps&stacks, MMU/ MPU)?

- How to identify most interesting tasks (3GPP Layer3 components doing message (IE) parsing)?

### Execution Mode

- Expected: typical OS with kernel+user space: many SVC calls in user-space code, complex SVC handlers and RETs in kernel code.

- Few SVC handlers implemented, mostly ramdumping and resets

- System registers indicate supervisor

- Preliminary conclusion\*: all supervisor, all the time:)

<sup>\*</sup> ultimately verified by issuing privileged instructions once we had RCE

### Task Identification

- tasks in ramdump make use of their stack frames

- find stacks in ramdump by stackframe analysis

- heuristic of a stack: dword == instr+1, instr follows a BL

- backtrace frames —> common task init function —> initialization routine fills in task struct, kept on linked lists

- taskscan.py walks linked list structure: #101 tasks

```

stack_top: 0x42f05b78 stack base: 0x42ef5b9c

entry function is LTE_TCPI_task_entry

task name is LTE SISO

stack top: 0x42f15b78 stack base: 0x42f05b9c

entry function is LTE_SISO task entry

task name is PacketHa2

stack top: 0x42d69110 stack base: 0x42d66934

entry function is

task name is MM

stack_top: 0x42d80880 stack_base: 0x42d7d8a4

entry function is MM task entry

task name is LLC

stack_top: 0x42e917f0 stack_base: 0x42e90814

entry function is LLC task entry

task name is recMailT

stack top: 0x42f6d378 stack base: 0x42f6cf9c

entry function is recMailT task entry

task name is DS MM

stack top: 0x42d8bc38 stack base: 0x42d88c5c

entry function is DS MM task entry

task name is DS LLC

stack top: 0x42e979b4 stack base: 0x42e969d8

entry function is DS LLC task entry

task name is LteRrc

stack_top: 0x42dfbff0 stack_base: 0x42dec014

entry function is

task name is REG_SAP

stack top: 0x42eb9b78 stack base: 0x42eb8b9c

entry function is REG SAP task entry

task name is SIM SAP

stack top: 0x42ebc378 stack base: 0x42ebbb9c

entry function is SIM_SAP_task_entry

task name is DS REG S

stack_top: 0x42ebe378 stack_base: 0x42ebd39c

entry function is DS REG S task entry

task name is Default

stack top: 0x42d55910 stack base: 0x42d55534

entry function is Default task entry

task name is CC

stack_top: 0x42d7d880 stack_base: 0x42d798a4

entry function is CC task entry

stack top: 0x42dabff0 stack base: 0x42d9c014

```

# Task Message Queuing

```

while (1)

74

75

76

v12 = get_incoming_msg_from_queue_struct(23, &ptr, &res, 1);// msg_queue_API, shared across all tasks

77

v44 = &unk \ 41CC7250;

78

v45 = 262213;

79

dbg_trace_args_something((unsigned __int64 *)&v44, -20071784);

++num_cc_in_messages;

80

v44 = &unk 41CC7544;

81

82

v45 = 262212;

83

dbg_trace_args_something((unsigned __int64 *)&v44);

84

if ( v12 )

85

break;

86

if ( (unsigned __int8)res != 2 )

87

88

if ( (unsigned int8)res == 3 )

// res == 3 seems to mean that it is a timer expiry event, res == 3 that it is a new

89

90

calls_HEDGE_NASL3_CC_cc_EctManagement_something__3((unsigned int)ptr);// sg related to timer expiry

91

92

else

93

94

v44 = &unk 41CC726C;

95

v45 = 262208;

96

dbg trace args something((unsigned int64 *)&v44);

97

98

curr_cc_msg = 0;

99

goto LABEL 14;

100

101

v13 = ptr;

102

curr cc msg = (int)ptr;

103

while (1)

// now process each stored message, if any

104

105

if ( v13 )

106

107

CC process msg();

// process incoming message

j_free(&curr_cc_msg, "../../HEDGE/NASL3/CC/Code/Src/cc_Main.c", (void *)0x1E2);

108

109

110 LABEL 14:

111

v14 = 0;

112

while (1)

113

114

v15 = (char **)stored cc msgs[2 * v14]; // some messages get stored away for later processing

v16 = *v15;

115

116

if ( *v15 )

117

break;

118

v14 = (unsigned __int8)(v14 + 1);

119

if (v14 >= 7)

120

goto LABEL 18;

121

122

*v15 = 0;

v44 = &unk & 41CC7560;

123

124

v45 = 262212;

125

dbg trace args something((unsigned int64 *)&v44, -20071784, stored cc msgs);

126 LABEL 18:

127

curr cc msg = (int)v16;

128

if (!v16)

129

break;

// rest of the outer while loop is timer and state mgmt

130

v13 = v16;

```

### RTOS Memory Management

- Task stacks:

- found easily from task structs

- static locations, always packed one after the other. Each stackframe's top includes two DEADBEEF markers.

- Heaps:

- y = malloc(x); memcpy(y, z, x) is a very frequent pattern.

relatively easy to spot. free, realloc found from there

- custom implementation. tl;dr: slot-based allocator for various sizes, with look-aside doubly-linked free lists

### Memory Configuration/\*PU?

- The ARM R7 has an MPU only (no MMU).

- MPU configured via MCR instructions; reuse scripting

- This yields a static struct in memory -> get segment permission values. Wrote another script to automate all that.

- Result: we know the permissions and type of every segment precisely now.

```

Configure_MPU

MCR p15, 0, R3,c6,c2, 0; Write MPU Region Number Register

MCR p15, 0, R0,c6,c1, 0; Write MPU Region Base Address Register

MCR p15, 0, R1,c6,c1, 2; Write MPU Region Size and Enable Register

MCR p15, 0, R2,c6,c1, 4; Write MPU Region Access Control Register

BX LR

```

main code regions start@0x04000000 and 0x40000000

# Memory Management

```

1 signed int initialize MPU_config()

int v0; // r0@1

signed int v1; // r4@1

int i; // r403

_DWORD *v3; // r1@4

unsigned int v4; // r0@5

_BOOL1 v5; // nf@5

unsigned _int8 v6; // vf@5

int v7; // ro@8

10

11

12

disable_instruction_cache();

sub_40E1CAF0();

13

sub_40E1CCAC(v0);

dword 2FOC = 19506;

15

16

v1 = \overline{0};

17

configure MPU wrapper(v1++, 0x80000000, 0x3A, 0x10, 0x300, 0x1000, 0, 0, 0, 0);//

18

19

// address 0x80000000

20

// size 0x3A

// permissions: 0x10, 0x300, 0x1000

21

22

// enable bit: 0

23

24

while ( v1 < 14 );

25

for (i = 0; ; ++i)

26

NEXT REGION

27

v4 = MPU_region_configs[10 * i];

Region num: 1

v6 = _{OFSUB}_{(v4, 255)};

28

DRBAR (R0): 0x04000000

v5 = ((v4 - 255) & 0x80000000) != 0;

29

DRSR (R1): 0x0000001f

if ( v4 != 255 )

30

DRACR (R2): 0x00000608

31

DRNR (R3): 0x00000001

32

v6 = _OFSUB_(i, 14);

-0x04010000

v5 = \overline{i} - 14 < 0;

Region addr:

33

2000)

34

Region size:

if (!((unsigned __int8)v5 ^ v6) )

35

Region enabled:

36

break;

Disabled subregions:

OL, OL, OL, OL, OL, OL]

37

v3 = &MPU region configs[10 * i];

Region share-able:

38

configure_MPU_wrapper(

Region XN:

39

Region AP:

Privileged: Read Only User: Read Only

40

v3[1],

Region TEX,C,B:

Outer and Inner Non-cachable Normal

41

v3[2],

NEXT REGION

42

v3[3],

43

*((_{QWORD} *)v3 + 2),

Region num: 2

*((_QWORD *)v3 + 2) >> 32,

44

DRBAR (RO): 0x04800000

45

v3[6],

DRSR (R1): 0x0000001b

46

v3[7],

DRACR (R2): 0x00001308

47

v3[8],

DRNR (R3): 0x00000002

48

v3[9]);

0x04800000-0x04804000

Region addr:

49

16 KB (0x00004000)

Region size:

50

enable instruction cache();

51

v7 = invalidate_data_cache();

Region enabled:

sub 40E1CCA8(v7);

Disabled subregions:

[OL, OL, OL, OL, OL, OL, OL, OL]

return sub_40335E50();

Region share-able:

Region XN:

d/Write User: Read/Write

Region AP:

Pri

Region TEX,C,B:

Out

er Non-cachable Normal

```

### Debugging Crashes

- screen shows crash information, including crash type. mildly useful.

- found register map structure in memory

- following the interrupt vector/ exception table we got really lucky here

- exception handling fills global register map

```

SAMSUNG

[ RST_STAT = 0x20000000 ]

EVT 1.3

ASV TBL VER = 15, Grade = A

ASV big:11 LITTLE:11 G3D:11 MIF:11 INT:11, CAM_DISP:11

LOT_ID = N2Y77

CHIP_ID = 07b72f98b388

CHIP_ID2 = 00003b00

ATLAS:37'C APOLLO:42'C G3D:41'C ISP:40'C

CP Crash CP_CRASH_RESET

UNTS: N/A

DATA ABORT

```

```

BYTE *dump reg values()

signed int v0; // r5@1

DWORD *v1; // r4@1

BYTE *result; // r0@4

v0 = 0;

print_0("iLine

: %d \n", dword_432BEFD4);

print_0("szFile : %s \n", dword_432BEFD8);

print_0("szError : %s \n", error_status_ptr);

: 0x%08X \n", dword_432BF1E8);

print_0("r0

print 0("r1

: 0x%08X \n", dword_432BF1EC);

print 0("r2

: 0x%08X \n", dword_432BF1F0)

print_0("r3

: 0x%08X \n", dword_432BF1F4);

print 0("r4

: 0x%08X \n", dword_432BF1FC);

: 0x%08X \n", dword_432BF1FC);

print 0("r5

print_0("r6

print 0("r7

: 0x*08X \n", dword_432BF208);

: 0x*08X \n", dword_432BF20C);

print 0("r8

: 0x*08X \n", dword_432BF210);

print 0("r10

: 0x%08X \n", dword_432BF214);

print 0("rl1

```

# Debugging Crashes

- screen shows crash information, including crash type. mildly useful.

- found register map structure in memory

- following the interrupt vector/ exception table we got really lucky here

- exception handling fills global register map

almost proper crash debugging

```

.data:432BF1E4 dword 432BF1E4

DCD Oxffff

DCD 0x40041

DCD 0

DCB

DCB

.data:432BF202

DCB

DCD OxFE

DCD 0x42521D4C

DCD 0x20000033

.data:432BF224 r13 sp usr

DCD 0x4803540

DCD 0

.data:432BF228 r14 lr usr

DCB 0x13

DCB

.data:432BF230 r13 sp svc

.data:432BF234 r14 lr svc

.data:432BF238 dword 432BF238

.data:432BF23C spsr abt

.data:432BF240 r13 sp abt

DCD 0x48035C0

.data:432BF248 spsr und

.data:432BF24C r13 sp und

.data:432BF254 r13 sp irq

.data:432BF258 r14 lr irg

DCD 0x400000C4

```

# Live Debugging

- SVE-2016-5301\* mentioned ability to unlock device via AT command

- AT command situation far worse than what authors released! (try AT+CLAC)

- modem read/write memory via AT commands among other things

- could also build a full debugger now... but we skipped that

```

Terminal ready

AT+HREGREAD=41422158

0x41422158=0xffffffff

OK

AT+HREGWRITE=41422158=42

OK

AT+HREGREAD=41422158

0x41422158=0x42

```

# Vulnerability Hunting

- implementation errors,

exploitable memory

corruptions

- "higher-level" involving parsing of messages we can send from a fake BTS/network

- NAS most fruitful, RRC short signaling messages

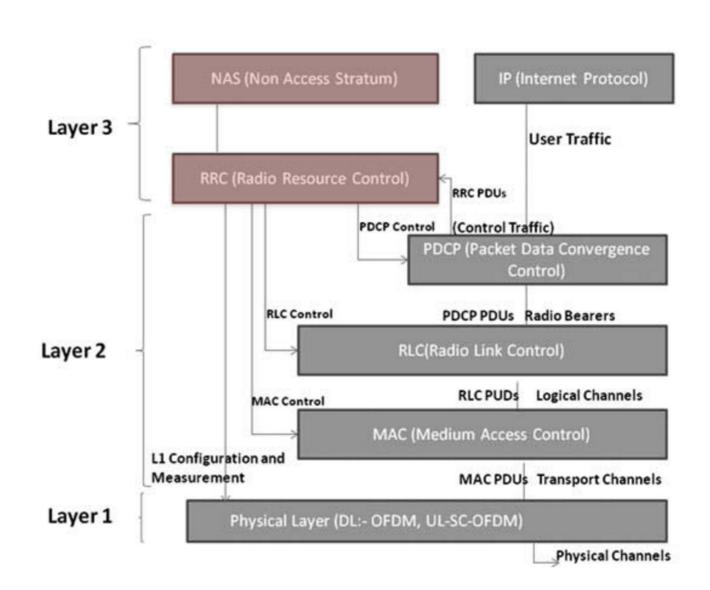

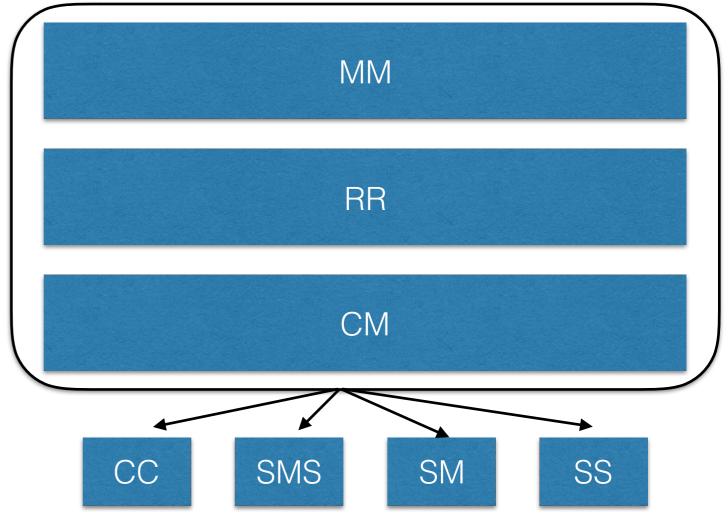

# Vulnerability Hunting / NAS

(non-GPRS)

- NAS responsibilities:

- Mobility Management (MM)

- Radio Resource Management (RR)

- Connection Management

- CM parses/processes/establishes

- calls (CC)

- short messages (SMS)

- USSD (SS)

- messages chain Information Elements (IEs)

- TLV-E (0-65535)

#### simplified LTE Layer 3

# Vulnerability Hunting / NAS

- two approaches:

- try to associate spec understanding with collected strings / IE parsing

- identify message processing in L3 stack

- Example L3/Call Control (CC) task loop:

- dequeue message

- CC\_process\_msg() -> parse IEs -> trigger callback (-> generate OTA response)

- free message

# CC\_process\_msg()

- CC\_process\_msg() operates on raw OTA Layer 3 message

- calls central parse\_IEs():

- parses IEs based on global IE definition arrays (type, IEI, min\_size, size)

- encapsulates messages into IE representation array <V\_ptr; LI; is\_present>

- dispatches handler from global array based on message id (useful for exploitation as well!)

- handlers work on IE representation array content

# CC\_process\_msg()

- 3GPP spec -> actual handler is trivial

- message ids are not 3GPP ids, but

- everything that contains "<RADIO MSG>" is one essentially

```

41301A4C aCcRadioMsgAlert_ind DCB "CC <== <RADIO MSG > ALERT_IND",0

; DATA XREF: .data:CC in msgs10

41301A4C

41301A69

41301A6C aCcRadioMsgModify ind DCB "CC <== <RADIO MSG > MODIFY IND",0

; DATA XREF: .data:CC in msgs10

41301A6C

41301A8A

ALIGN 4

41301A8C aCcRadioMsgNotify ind DCB "CC <== <RADIO MSG NOTIFY IND",0

; DATA XREF: .data:CC in msgs10

41301A8C

41301AAA

ALIGN 4

41301AAC aCcRadioMsgFacility_ind DCB "CC <== <RADIO MSG > FACILITY_IND",0

; DATA XREF: .data:CC in msgsfo

41301ACC aCcVcg_callestablish_cnf DCB "CC <== VCG_CALLESTABLISH_CNF",0

; DATA XREF: .data:CC in msgsfo

41301ACC

41301AE9

41301AEC aCcVcg_altercodec_cnf DCB "CC <== VCG_ALTERCODEC_CNF",0

; DATA XREF: .data:stru 41042CB41o

41301AEC

41301B06

ALIGN 4

41301B08 aCcCc alert ind DCB "CC ==> CC ALERT IND", 0 ; DATA XREF: .data:CC out msgs o

DCB "CC ==> CC AOC IND",0 ; DATA XREF: .data:stru 41042CD010

41301B1C aCcCc aoc ind

41301B2E

ALIGN 0x10

```

## Finding Exploitable Bugs

- At this point we know:

- all OTA handlers

- structure of incoming payloads; tainted values (payload, len with the constraints)

- Further vulnerability hunting options:

- manual handler analysis and IDA scripting, looking for tainted length in memcpy etc.

- bjoern, decompiler+joern, ...

- Can't estimate how "buggy" this code is: we found a winner quickly, weren't forced to do more vuln hunting

# So you want to fuzz basebands?

- We don't recommend OTA live fuzzing at all!

- Researchers developed fuzzers and found bugs, but:

- basebands are more fragile than you think: hangs and weird behavior are normal during test

- often implement spec loosely or only subset

- state machines are complex, especially in error/repetition cases

- a significant amount of corruptions do not result in good crashes

#### SVE-2015-5123: Samsung Galaxy Edge baseband process vulnerability

Severity: Critical

Affected versions: Selected models including Galaxy S6/S6 Edge, Galaxy S6 Edge+, and Galaxy Note5

with Shannon333 chipset

Reported on: November 12, 2015

Disclosure status: This issue is publicly known. (CVE-2015-8546)

A vulnerability generating a stack overflow enables an attacker to run remote codes on the vulnerable

devices by pushing a malicious code from a fake base station.

The supplied patch prevents a stack overflow problem.

#### SVE 2015-5123: Samsung Galaxy Edge baseband process vulnerability

Severity: Critical

Affected versions: Selected modern Schuding Galaxy S6/S6 Edge, Galaxy S6 Edge+, and Galaxy Note5

with Shannon333 chipset

Reported on: November 12, 2015

Disclosure status: This issue is publicly known (CVE-2015-85-0).

A vulnerability generating a stack over low enables an attacker to run remediated so the vulnerable devices by pushing a malicipal code from a fake base station.

The supplied patch wents a stack overflow problem.

#### Description:

As described in 3GPP TS 24.008, the serving cellular network can send a "PROGRESS" message (see 9.3.17) to the UE. The standard makes it mandatory to include a "Progress Indicator" Information Element (IE) within this message. This IE is a length/value element, which is specified in 10.5.4.21. From the specification: "The purpose of the progress indicator information element is to describe an event which has occurred during the life of a call."

When the cellular baseband (CP) is parsing this message, it is not properly guarding against a stack-based buffer overflow when copying Progress Indicator elements to a local stack buffer. This can result in memory corruption and as a result, yield to arbitrary code execution by an adjacent attacker who runs the serving network.

```

CC_decodeProgressInd

{

sub_404EAEF4((char *)(unsigned __int8)in

if ( is_progress_ind_set() == 1 )

{

copy_progress_ind((int)&v24);

v15 = return_progress_ind_len();

v12 = v15;

v16 = v25 & 0x7F;

v16 = v25 & 0x7F;

return_memcpy_8(a1, Progress_Ind_IE_repr.V_ptr, (unsigned __int16)Progress_Ind_IE_repr.LI);

}

```

literally a text book stack-based buffer overflow over-the-air!

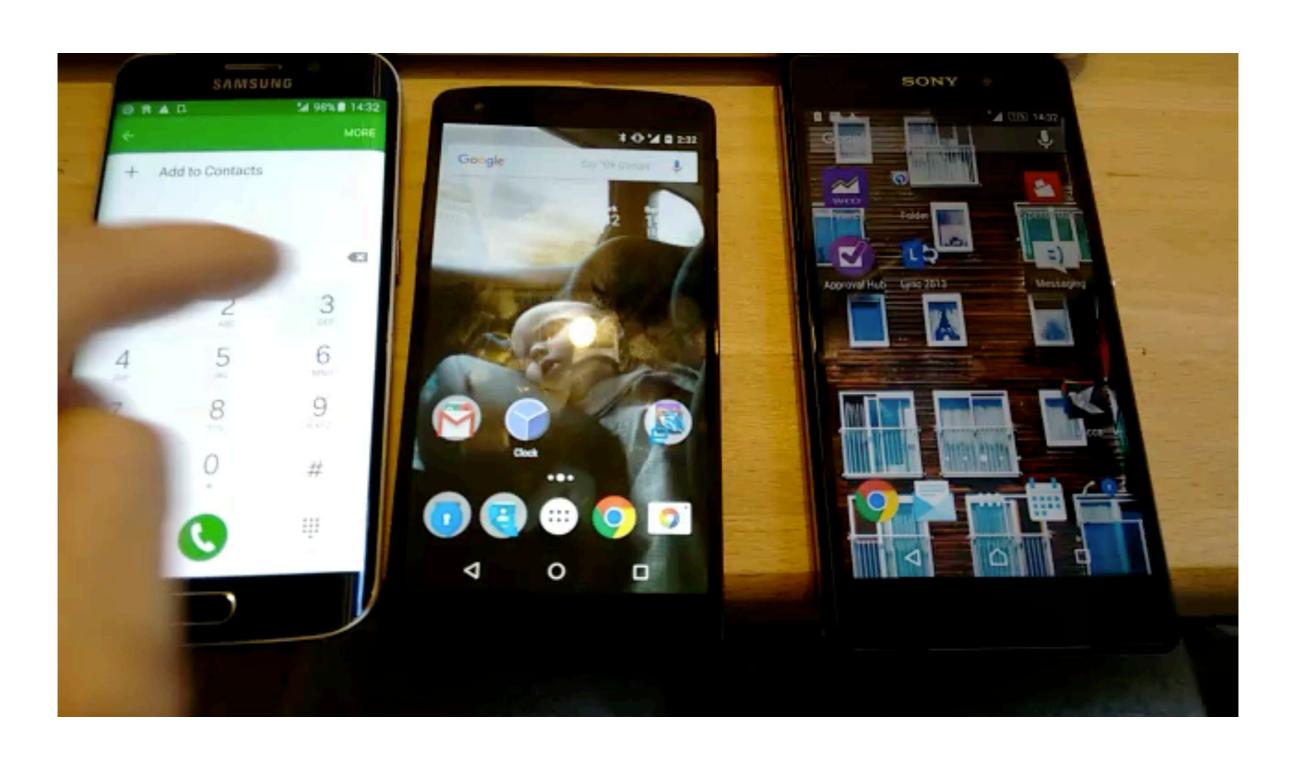

### DEMO

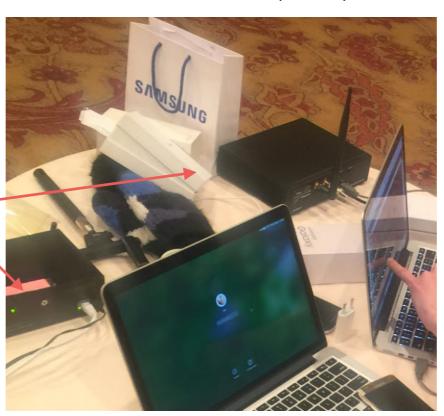

# Exploitation / Setup

- OpenBSC provides FOSS network stack (GSM)

- stuff messages into gsm48\_conn\_sendmsg()

- many options for Base Transceiver Station (BTS) side:

- nanoBTS,

- sysmoBTS

- SDR (USRP,..)

- •

- < <500 \$

# Exploit Mitigations

#### Existing mitigations/stability improvements

- stack overflows are checked (verifies the deadbeef markers during task scheduling switches)

- heap guard words exist

- R7 supports XN and is configured for certain regions by the MPU

#### Lack of baseline mitigations

- stack/heap guards static, no heap hardening (safe unlinking, ...)

- no stack canaries

- no randomization / static unprotected function pointers

#### · Broken mitigations:

• the XN region configuration is broken/incomplete: e.g. stack/heap not one of them

## Exploit Primitives

- Content at static or less fluctuant address (some):

- short-term subscriber identity/TMSI -> known dword

- network name (long/short) -> alphanumeric ARM shellcode (also uncached!)

- Payload size restrictions: bypass via staged CC/L3 handler hooking

- Clean state returns: L3 state machines are simple loops -> jump to the beginning automatically processes next message (assuming registers are setup correctly)

- **Persistence**: clean return survives flight mode toggle; potential path for real persistence may exist (e.g. exploiting nv item parsing issues etc.)

# Exploit Payloads

- baseband code execution has limited functionality

- **not** the master over application processor/memory (these days), but loaded by apps processor! (pls get this right in public debates)

- baseband sees all\* data/signaling exchanged with cellular networks though (calls, text messages, data)

- typical payloads would alter/eavesdrop/inject/drop these

- for our demo we have chosen to reroute calls (e.g. for MitM): simple payload that changes signaling data (<100 bytes); implanted via patching callback code

# Exploitation Fails

#### Caching

- making RX code RWX via MPU config works ...but actual patching works unreliably; somehow cache flushing MCRs don't work as expected (maybe LLI related?)

- eventually went for patching data, not code

#### Dual-Sim code snafus

- almost the entire L3 code is duplicated in the firmware, with "DS\_" labels added to names

- we suspect this is a primitive dual-sim support implementation.

- tl;dr: verify bindiff results with care when upgrading firmware versions!

### Application Processor Escalation

#### modifying application processor data traffic:

• inject JS into HTML or relay traffic to attacker controlled site -> browser pwn or exploit an unsecured update process (e.g. SwiftKey Keyboard, ...)

#### · IPC channels:

- shared memory IPC implementation (parsing, range checking, ..)

- DMA capable peripherals (data moving)

- services built on top of this (e.g. RILD\*)

- IPC/LLI message debugging on Android via /d/svnet/mem\_dump

- full baseband<->apps IPC traces, including your seen networks, called numbers, etc

- yes, this is available to unprivileged applications on Galaxy devices!

\* the old remoteFS directory traversal bug discussed by Replicant seems fixed;)

### Final Remarks

- 2 people / part time effort; 3-6 months

- basebands are also "just" embedded systems, no mad ninja skills required

- still a lot of space for research, especially on exploitation:

- target identification (device/firmware)

- application processor escalation

### Tools Release

- github.com/comsecuris/shannon (release imminent:)

- 010 Editor templates

- IDA loaders

- RAMDUMP scripts

- idapython: scanning tasks, naming functions, MPU configuration, register dumps, read/write memory, unpack modem binaries, naming of message handlers etc.

### Questions

contact@comsecuris.com

# Backup - Relaying of Calls / Impact

Comsecuris

- Essentially enables interception/MitM of calls

- Attacker would just need to know original number to initiate new call and proxy

- Options:

- append original number to caller and extract on attacker side

- 3GPP provides "called party subaddress" field to denote extensions

- no visible behavior difference from user side (network can see this though)